Про ASIC-и, FPGA-сики и ProASIC-и...

Поскольку альтернативного, экономически-целесообразного и энергетически-эффективного решения для высокопроизводительных вычислений, акромя использования микросхем программируемой логики (ПЛИС) или заказных СБИС (ASIC), в настоящее время не просматривается, то надо к ним повнимательнее приглядеться ... Информации по теме ПЛИС достаточно много на просторах интернета и в печатном виде, но она разбросана либо по отдельным производителям, либо освещает лишь некоторые аспекты. Решил создать здесь широкий обзор тематики, так как на мой взгляд, у многих интересующихся прикладным применением устройств для майнинга, наблюдается недостаток информированности об этих устройствах и используемых в них технологиях. Многие очевидно считают, что технология ASIC это более совершенный вариант реализации FPGA-технологии. Ничего подобного ! Обывательские разговорчики. (с). Итак, попробуем поковыряться у них в "кишках" и разобраться что к чему.

Программируемые логические интегральные схемы (ПЛИС) – один из продуктов прогресса микроэлектронной промышленности, применяемый для реализации всевозможных цифровых устройств самой разной сложности. Появились они около 20-ти лет назад и быстро завоевали лидерство в области разработки схемных решений для цифровых устройств. Основные производители ПЛИС: корпорации "Altera", "Xilinx", "Lattice semiconductor", "Actel".

Диапазон применения ПЛИС очень широк: от простых счетчиков и преобразователей кодов, несложных цифровых схем, ранее реализуемых на рассыпухе до специализированных вычислителей или различных процессоров, вплоть до создания нейронной сети.

Таким образом, некоторое цифровое устройство, которое было разработано лет 15-20 назад, располагалось на десятке плат и занимало целую корзину в монтажной стойке, теперь может быть реализовано на одной небольшой печатной плате. Мало того: при использовании ПЛИС появляется возможность без особых усилий и затрат изменить функциональную наполненность всего цифрового устройства - путем изменения конфигурации ПЛИС. Чего раньше (при использовании дискретных логических микросхем (рассыпуха)) невозможно было сделать без доработки и изменения устройства. Зачастую проще было разработать новое устройство, чем дорабатывать и доводить до ума старое.

Как пример реализации оборудования с заменой устаревшей элементной базы на относительно дешевую и небольшую ПЛИС + небольшой микроконтроллер, приложу видео с моим прожектом модернизации итальянского упаковочного автомата 30-летнего возраста. Здесь вся электронная система управления, занимавшая небольшой шкафчик, уместилась в маленькую симпатичную коробочку. Некоторое врямя этот девайс успешно работал. Жаль только, что фабрика та сгорела к монахам вскоре после пробных испытаний устройства ...

Программируемые логические интегральные схемы (ПЛИС) – один из продуктов прогресса микроэлектронной промышленности, применяемый для реализации всевозможных цифровых устройств самой разной сложности. Появились они около 20-ти лет назад и быстро завоевали лидерство в области разработки схемных решений для цифровых устройств. Основные производители ПЛИС: корпорации "Altera", "Xilinx", "Lattice semiconductor", "Actel".

Диапазон применения ПЛИС очень широк: от простых счетчиков и преобразователей кодов, несложных цифровых схем, ранее реализуемых на рассыпухе до специализированных вычислителей или различных процессоров, вплоть до создания нейронной сети.

Таким образом, некоторое цифровое устройство, которое было разработано лет 15-20 назад, располагалось на десятке плат и занимало целую корзину в монтажной стойке, теперь может быть реализовано на одной небольшой печатной плате. Мало того: при использовании ПЛИС появляется возможность без особых усилий и затрат изменить функциональную наполненность всего цифрового устройства - путем изменения конфигурации ПЛИС. Чего раньше (при использовании дискретных логических микросхем (рассыпуха)) невозможно было сделать без доработки и изменения устройства. Зачастую проще было разработать новое устройство, чем дорабатывать и доводить до ума старое.

Как пример реализации оборудования с заменой устаревшей элементной базы на относительно дешевую и небольшую ПЛИС + небольшой микроконтроллер, приложу видео с моим прожектом модернизации итальянского упаковочного автомата 30-летнего возраста. Здесь вся электронная система управления, занимавшая небольшой шкафчик, уместилась в маленькую симпатичную коробочку. Некоторое врямя этот девайс успешно работал. Жаль только, что фабрика та сгорела к монахам вскоре после пробных испытаний устройства ...

Сегодня ПЛИС делятся на две основные группы: CPLD(Complex Programmable Logic Device) и FPGA(Field-Programmable Gate Array).

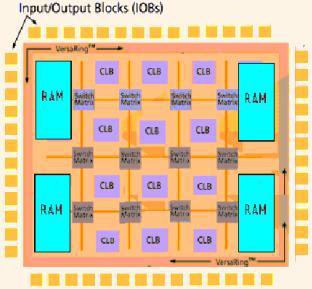

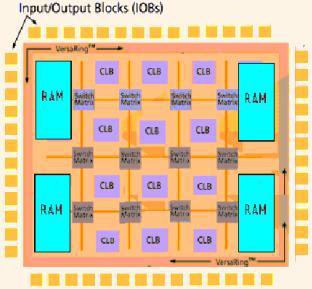

В буквальном переводе, первая группа - это Сложные Программируемые Логические Устройства, а вторая - Программируемая Пользователем Вентильная Матрица. CPLD как и FPGA структурно состоят из матрицы логических блоков, матрицы соединений, блоков ввода-вывода и конфигурационной памяти, хранящей топологию связей между логическими блоками.

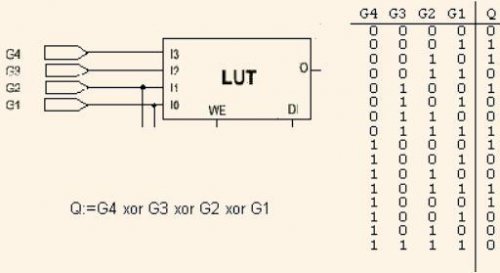

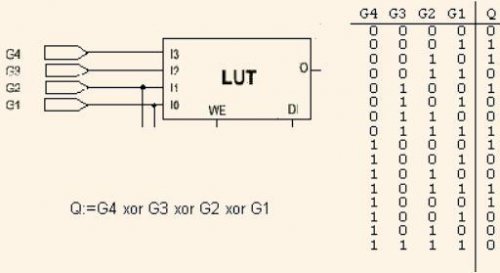

Принципиальная разница между ними в том, что у CPLD базовый слой содержит укрупненные логические блоки на основе элементарных вентилей (2И-НЕ/2ИЛИ-НЕ), а у FPGA этот слой содержит более компактные логические ячейки на основе таблиц истинности (LUT) и количество логических ячеек в базовом слое FPGA превышает количество онных в CPLD на 1-2 порядка. Вследствие этого FPGA имеет более гибкую архитектуру.

Также необходимо добавить, что FPGA в отличие от CPLD, могут содержать на базовом слое специальные ядра, ускоряющие специфические алгоритмы обработки (DSP-блоки), а также блоки памяти. Процесс программирования ПЛИС заключается в переносе конфигурации матрицы соединений на специальную внутреннюю память ПЛИС. В этом аспекте CPLD и FPGA (почти все) заметно отличаются. Если CPLD содержит прямо на кристалле энергонезависимую конфигурационную память, но с ограниченным количеством циклов программирования, то почти все представители семейства FPGA содержат на кристалле блок энергозависимого ОЗУ в качестве конфигурационной памяти. Данную память при старте системы нужно загрузить конфигурационной информацией, которая обычно располагается во внешнем ППЗУ (параллельного или последовательного типов).

Данная технология загрузки конфигурации с внешней памяти практически не имеет ограничения на количество циклов программирования, т.к. современные Flash-ППЗУ допускают до 100 000 циклов перезаписи. Но данная технология имеет один серьезный недостаток: она требует некоторого времени для загрузки конфигурации и при этом процессе происходит заметный бросок потребляемого системой тока, что создает дополнительные требования к цепям питания и фильтрации. Такую технологию конфигурирования (SRAM-технологию) поддерживают почти все FPGA. Но... не все. Если FPGA-чипы основных мировых производителей "Altera" и "Xilinx" построены на данной технологии, то FPGA-чипы менее именитого производителя - корпорации "Actel", построены по FLASH-технологии конфигурационной памяти. Это значит, что свою конфигурацию эти FPGA сохраняют и при выключенном питании, а при включении - данный тип FPGA мгновенно готов к работе. Кроме того, данная технология конфигурирования FPGA не только избавлена от начальных бросков тока при загрузке, но и сокращает энергопотребление кристалла, а также в несколько раз уменьшает размеры конфигурационной ячейки, что позволяет более эффективно использовать площадь кристалла. Вообще говоря, FPGA от "Actel" представляются наиболее интересными для использования под майнинг ввиду привлекательных цен и хорошей энергоэффективности. На них я остановлюсь подробнее чуть ниже.

Корпорация "Lattice semiconductor" избрала третий (гибрридный) вариант реализации конфигурирования FPGA: у них также как у "Altera" и "Xilinx" задействована SRAM-технология загружаемой конфигурирации, но FLASH-память конфигурации расположена не снаружи, а внутри кристалла.

Выпускаемые FPGA делятся по ценовому и функциональному критериям на несколько сегментов: нижний, средний и топовый. У корпорации "Altera" разные сегменты FPGA представлены такими семействами как Cyclone(нижний), Arria(средний) и Stratix(топовый). У корпорации "Xilinx" до недавного времени было два сегмента, которые были представлены семействами Spartan(нижний) и Virtex(топовый). На данный момент между ними расположились еще два: Artix и Kintex.

В буквальном переводе, первая группа - это Сложные Программируемые Логические Устройства, а вторая - Программируемая Пользователем Вентильная Матрица. CPLD как и FPGA структурно состоят из матрицы логических блоков, матрицы соединений, блоков ввода-вывода и конфигурационной памяти, хранящей топологию связей между логическими блоками.

Принципиальная разница между ними в том, что у CPLD базовый слой содержит укрупненные логические блоки на основе элементарных вентилей (2И-НЕ/2ИЛИ-НЕ), а у FPGA этот слой содержит более компактные логические ячейки на основе таблиц истинности (LUT) и количество логических ячеек в базовом слое FPGA превышает количество онных в CPLD на 1-2 порядка. Вследствие этого FPGA имеет более гибкую архитектуру.

Также необходимо добавить, что FPGA в отличие от CPLD, могут содержать на базовом слое специальные ядра, ускоряющие специфические алгоритмы обработки (DSP-блоки), а также блоки памяти. Процесс программирования ПЛИС заключается в переносе конфигурации матрицы соединений на специальную внутреннюю память ПЛИС. В этом аспекте CPLD и FPGA (почти все) заметно отличаются. Если CPLD содержит прямо на кристалле энергонезависимую конфигурационную память, но с ограниченным количеством циклов программирования, то почти все представители семейства FPGA содержат на кристалле блок энергозависимого ОЗУ в качестве конфигурационной памяти. Данную память при старте системы нужно загрузить конфигурационной информацией, которая обычно располагается во внешнем ППЗУ (параллельного или последовательного типов).

Данная технология загрузки конфигурации с внешней памяти практически не имеет ограничения на количество циклов программирования, т.к. современные Flash-ППЗУ допускают до 100 000 циклов перезаписи. Но данная технология имеет один серьезный недостаток: она требует некоторого времени для загрузки конфигурации и при этом процессе происходит заметный бросок потребляемого системой тока, что создает дополнительные требования к цепям питания и фильтрации. Такую технологию конфигурирования (SRAM-технологию) поддерживают почти все FPGA. Но... не все. Если FPGA-чипы основных мировых производителей "Altera" и "Xilinx" построены на данной технологии, то FPGA-чипы менее именитого производителя - корпорации "Actel", построены по FLASH-технологии конфигурационной памяти. Это значит, что свою конфигурацию эти FPGA сохраняют и при выключенном питании, а при включении - данный тип FPGA мгновенно готов к работе. Кроме того, данная технология конфигурирования FPGA не только избавлена от начальных бросков тока при загрузке, но и сокращает энергопотребление кристалла, а также в несколько раз уменьшает размеры конфигурационной ячейки, что позволяет более эффективно использовать площадь кристалла. Вообще говоря, FPGA от "Actel" представляются наиболее интересными для использования под майнинг ввиду привлекательных цен и хорошей энергоэффективности. На них я остановлюсь подробнее чуть ниже.

Корпорация "Lattice semiconductor" избрала третий (гибрридный) вариант реализации конфигурирования FPGA: у них также как у "Altera" и "Xilinx" задействована SRAM-технология загружаемой конфигурирации, но FLASH-память конфигурации расположена не снаружи, а внутри кристалла.

Выпускаемые FPGA делятся по ценовому и функциональному критериям на несколько сегментов: нижний, средний и топовый. У корпорации "Altera" разные сегменты FPGA представлены такими семействами как Cyclone(нижний), Arria(средний) и Stratix(топовый). У корпорации "Xilinx" до недавного времени было два сегмента, которые были представлены семействами Spartan(нижний) и Virtex(топовый). На данный момент между ними расположились еще два: Artix и Kintex.

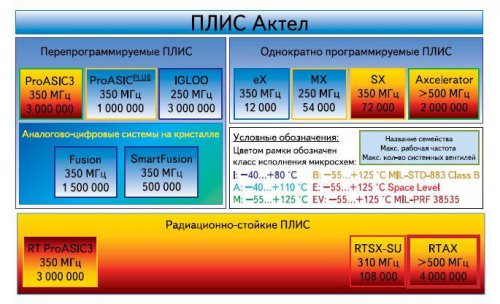

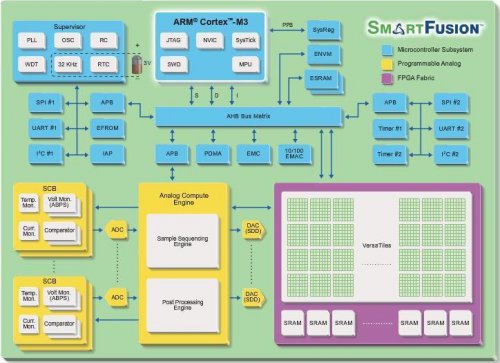

Как ранее было обещано, остановлюсь подробнее на уникальных в своем роде FPGA-представителях небольшой корпорации "Actel", которая насчитывает не более тысячи сотрудников по всему миру. Номенклатура ПЛИС, выпускаемых корпорацией "Actel", весьма широка и разнообразна: от "классических" FPGA в лице семейств ProASIC, ProASICPLUS, ProASIC3 до систем на кристалле (SoC), в лице семейств Fusion, SmartFusion и SmartFusion2. Линейка чипов семейства Fusion представляют собой нечто уникальное на сегодняшний день в области микроэлектроники - это объединение на одном кристалле внушительного блока ПЛИС, блока конфигурируемой аналоговой обработки, блоков ОЗУ, Flash-ПЗУ и даже встроенного CortexM3-контроллера с архитектурой ARM7 (присутствует в SmartFusion) !!! Таким образом на базе SmartFusion можно получить недорогое одночиповое и почти универсальное решение для построения широкого спектра управляющих, вычислительно-измерительных или коммутационных систем при вполне доступной стоимости в диапазоне от 20 до 50 у.е. Также стоит обратить внимание, что корпорация "Actel" единственная, кто выпускает уникальные серии радиационно-стойких ПЛИС, востребованных в аэро-космической отрасли и военно-промышленном комплексе.

В отличие от всех других производителей FPGA-чипов, которые используют технологию SRAM (статического ОЗУ) конфигурирования чипа, "Actel" использует Flash-технологию для непосредственного хранения информации о конфигурации внутри элементарной ячейки FPGA. Отсюда вытекают основные преимущества FPGA-чипов производства "Actel" перед другими производителями: отсутствие необходимости переноса конфигурационной информации из внешнего энергонезависимого ППЗУ в коммутационную матрицу на основе статического ОЗУ; отсутствие бросков тока потребления при включении устройства, наблюдаемым при загрузке FPGA-чипов SRAM-технологии; отсутствие задержки при включении устройства, связанной с загрузкой конфигурации. Ну и самое главное преимущество FPGA от "Actel" - это повышенная надежность изделий данного производителя. FLASH-ячейка конфигурации в отличии от SRAM-ячейки на несколько порядков устойчивее к сбоям и рискам изменения конфигурации, вызванными, к примеру, влиянием электромагнитных помех. На рисунках ниже изображены схемно и как фрагмент топологии, ячейки конфигурационной матрицы, выполненные по SRAM-технологии и по FLASH-технологии.

Поскольку в элементарной ячейке памяти FLASH-типа используется всего 1 транзистор с плавающим затвором, то размеры ячейки уменьшаются и площадь, занятая такой ячейкой на кристалле, приблизительно в 7 раз меньше площади, занимаемой SRAM-ячейкой. Как следствие этого, снижается суммарный ток потребления кристалла и растет быстродействие таких микросхем. Технология FLASH-ПЛИС позволяет изготавливать микросхемы с рекордно низкими уровнями потребления в статическом режиме. На приведенных рисунках хорошо видны энергетические преимущества FPGA-чипов, изготовленных по FLASH-технологии перед аналогами, выполненными на SRAM-технологии.

Еще одно очень важное преимущество в использовании FLASH-технологии конфигурирования FPGA состоит в том, что в данном случае становится невозможно скопировать битовый поток конфигурационной информации, идущий в момент загрузки конфигурации от внешнего ППЗУ к FPGA. Для защиты интеллектуальной собственности проектов, в случае использования FPGA выполненных по SRAM-технологии, разработчикам приходится прибегать к различным схемно-программным ухищрениям. К примеру: типа установки дополнительных контроллеров или CPLD, шифрующих битовый поток данных либо подключать резервный источник питания для FPGA, обеспечивающий питание конфигурационной памяти в режиме микропотребления.

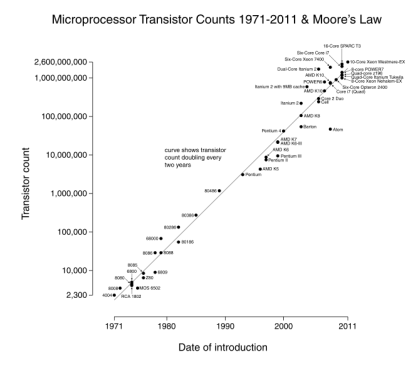

Техпроцесс изготовления сегодняшних FPGA (как и других устройств микроэлектроники) достиг уже 20-нм норм. А в ближайшей перспективе гигант микроэлектроники "Intel" собирается выпускать на своих заводах FPGA-чипы от "Altera" с нормами текхпроцесса 14 нм. Трудно себе даже представить масштабы прогресса микроэлектороники за прошедшие три десятка лет: первые микросхемы, выпущенные в 1979 году все тем же Intel, были разработаны на базе техпроцесса 3 мкм. Т.е. размеры элементарных структур микросхем уменьшились за это время более чем в 150 раз !!! Это позволяет сегодня размещать на кристаллах топовых семейств FPGA до десятка миллиардов транзисторов. Для сравнения: у 6-ти ядерного процессора Intel Sandy Bridge E (6C) насчитывается чуть более 2 млрд. транзисторов на кристалле. Согласно закону Мура, количество транзисторов, размещаемых на кристалле интегральной схемы, удваивается через каждые два года. Но сегодняшние технологии уже позволиили почти приблизиться к физическим пределам миниатюризации электронных схем. Еще совсем недавно уровень интеграции микросхем описывался понятиями БИС(большие интегральные схемы) и СБИС(сверхбольшие интегральные схемы), что соответствует сотням тысяч и нескольким миллионам логических вентилей на кристалле (вентиль реализуется на 4-ех эквивалентных транзисторах). Сейчас на некоторых чипах уже начитываются сотни миллионов вентилей на кристалле.

Мда... Так вот, вернемся к нашим

Если основных представителей СБИС - таких как CPU и ПЛИС можно отнести к стандартному и программируемому пользователем типам, то на противоположном «полюсе» технологии СБИС располагаются ASIC(Application-Specific Integrated Circuit), т.е. разрабатываемые только для выполнения конкретных задач пользователя - заказные микросхемы. Это, как правило, крупносерийные устройства типа "система на кристалле", заказываемые производителями электроники для удешевления своих изделий. Непосредственное серийное производство ASIC-чипов обходится намного дешевле, чем производство FPGA-чипов - в силу отсутствия дорогостоящей SRAM-конфигурационной памяти или в случае FPGA от "Actel" - более дешовой Flash-памяти. Но процесс подготовки производства нового ASIC-чипа несоразмерно дороже и длительнее, чем в случае разработки нового семейства FPGA. С точки зрения конечного пользователя, ASIC-чипы в отличии от FPGA, не нуждаются в загрузке конфигурационной информации и следовательно отсутствует возможность скопировать интеллектуальную собственность проекта внутри микросхемы ASIC. Также как и FPGA, микросхемы ASIC могут иметь встроенные блоки быстродействующей памяти. ASIC-микросхемам не грозит частичный сбой конфигурации, как в случае с FPGA, изготоленных по SRAM-технологии, так как связи межсоединений внутри ASIC-микросхемы непосредственные и неупраляемые. Но за все эти преимущества приходится платить длительными сроками разработки и внушительными бюджетами подготовки производства. Применение микросхем ASIC становится экономически оправданным в случае достаточно большого тиража продукции, так как финансово-трудовые издержки, затраченные на разработку и отладку проекта заказчика очень масштабны. Поскольку требуется очень тщательная верификация проектов, то и сроки отладки проектов могут быть намного больше, чем при отладке проектов для FPGA. Еще один недостаток (пожалуй, самый серьезный...) микросхем ASIC связан с тем, что они не могут быть переконфигурированы. Поэтому любая модернизация изделия, содержащего на борту ASIC-микросхемы, сопряжена со значительными трудностями.

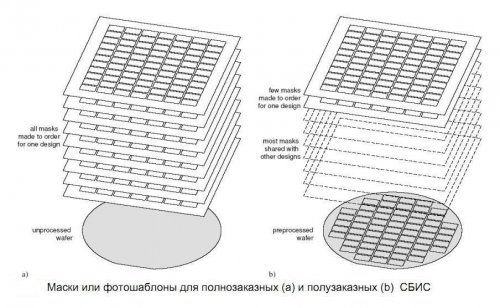

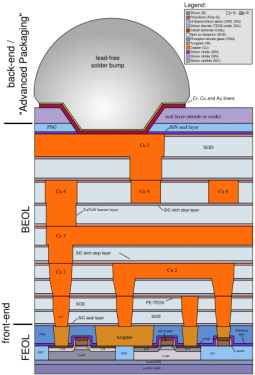

Все СБИС (включая CPU, ПЛИС и ASIC) имеют структуру слоистого коржевого торта. Эти "коржики" изготавливаются при помощи фотошаблонов (или масок). В современных техпроцессах при производстве СБИС может применяться до полусотни масок, определяющих базовые структуры, слои металлизации и изоляции. Самые нижние базовые слои содержат минимальные конструктивные элементы структуры - транзисторы. Следующие слои содержат наборы металлических проводников, определяющих топологию соединений для формирования базовых логических блоков (вентили, триггеры, сумматоры) и слои изоляции. А далее весь этот "тортик"

Процесс изготовления масок-фотошаблонов очень дорогой и длительный: Например, для техпроцесса 45 нм стоимость комплекта масок может достигать миллиона долларов и выше, а суммарный срок разработки и подготовки производства ASIC-чипа может составлять более года.

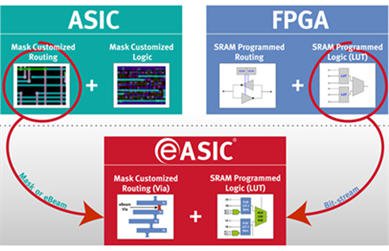

Различают ASIC-микросхемы полностью заказные (Full Custom) и полузаказные (Semi-Custom). Первые разрабатываются с нуля, т.е. начиная с разработки базовых транзисторных слоев. Вторые разрабатываются на основе базовых логических блоков и требуют только изготовления необходимых слоев металлизации и изоляции. При изготовлении Full Custom ASIC-микросхем разработчик имеет полную свободу действий и схемотехнических решений. В разультате на выходе могут быть получены наилучшие технические характеристики (быстродействие, энергоэффективность) и наилучшая степень использования кристалла. Полузаказные ASIC-микросхемы, в свою очередь изготавливаются на:основе вентильных матриц либо набора стандартных ячеек. Полузаказные ASIC на основе стандартных ячеек требуют изготовления полного комплекта фотошаблонов, но используют элементы стандартных библиотек схемных решений. Таким образом упрощается и удешевляется процесс изготовления базового слоя (базовый кристалл), что значительно сказывается на общей картине подготовки технологического процесса. По сравнению с Full Custom ASIC, эти полузаказные СБИС имеют менее выдающиеся технические характеристики, но позволяют вдвое уменьшить сроки разработки. При технологии полузаказных ASIC на основе вентильных матриц используются готовые стандратные схемные полуфабрикаты, называемые базовыми кристаллами, которые дополняются слоями межсоединений. В даном случае требуется изготовить гораздо меньшее количество фотошаблонов. Результирующие технические характеристи такого чипа получаются еще дальше от оптимума, но сроки разработки могут быть сокращены в трое-четверо. На сегодняшний день полузаказные ASIC-микросхемы эволюционировали в отдельный подвид сруктурированных ASIC, которые могут включать в свою структуру функционально завершенные блоки, как то: ядра процессоров, различные контроллеры или модули памяти. В этом сегменте есть весьма интересное решение, разработанное корпорацией "eASIC" - новое поколение структурированных ASIC-чипов под названием Nextreme. По заявлениям корпорации "eASIC", структурированные ASIC Nextreme позволяют сократить срок разработки до 1 месяца при отсутствии ограничения на минимальное количество выпускаемых изделий, имея при этом FPGA-подобную архитектуру ! Но о них я пожалуй расскажу отдельно другим разом, а то и так уже "многа букафф"

Некоторые корпорации, специализирующиеся на выпуске ПЛИС, также выпускают полузаказные ASIC, на основе свох базовых матричных кристаллов - например, серия HardCopy от "Altera" позиционируется как более дешевое решение в проектах, использующих FPGA-кристаллы топового семейства Stratix (II - V). К слову, HardCopy могут использоваться как прямая замена данных FPGA-чипов от "Altera", так как они полностью повторяют архитектуру соответствующих FPGA-чипов и совместимы по расположению выводов. Если сравнивать технические характеристики полузаказных ASIC и FPGA на примере тех же HardCopy и их FPGA-прототипов, то тут улучшение основных показателей может достигать до 50%. В большей степени это обусловлено непосредственными связями внутри кристалла и межсоединений, так как уменьшаются длины участков соединений и уменьшаются задержки распространения сигналов. Следовательно увеличивается быстродействие и уменьшается энергопотребление ASIC-чипов

Подведем итоги:

1. FPGA-чипы:

+ являются универсальным схемотехническим решением и могут быть легко и быстро адаптированы под выполнение практически любой задачи или алгоритма

- уступают по основным техническим характеристикам полузаказным и тем более полностью заказным ASIC-ам. Относительно дороги чипы топовых серий

2. ASIC-чипы:

+ хороши только для строго конкретных задач, под которые они и изготовлены, обладая при этом наилучшими показателями в сравнении с другими возможными решениями. Наименьшее энергопотребление и наибольшее быстродействие. Низкая себестоимость.готовых чипов.

- астрономически дороги на этапе подготовки производства и могут себя быстро окупить только при масштабных тиражах. Длительный процесс подготовки производства. Заказываются только большими партиями (десятки тысяч штук)

3. Применительно к майнингу, конечно же ASIC-и весьма заманчивы, но на мое IMHO - как-то это все очень сомнительно и маловероятно... Full Custom ASIC-микросхемы могут себе позволить немногие производители электроники. Так что, в данном контексте могут всерьез рассматриваться разве что полузаказные ASIC-чипы типа HardCopy от Altera. Но, опять же, смотря с какими тиражами работать.

Ну вот вроде бы и все, чем хотелось поделиться. Надеюсь что информация будет многим полезна ...

Оригинальная статья здесь.

Написано Николай III, 10 March 2013

Литература:

http://www.kit-e.ru/...2003_02_116.php

http://www.russianel...r/pechat/43923/

Литература:

http://www.kit-e.ru/...2003_02_116.php

http://www.russianel...r/pechat/43923/